# Lab Lecture for Lab #4 Pipelining Your Processor

Jack Kang cs152-ta@imail.eecs.berkeley.edu

Fall 2003 © UCB

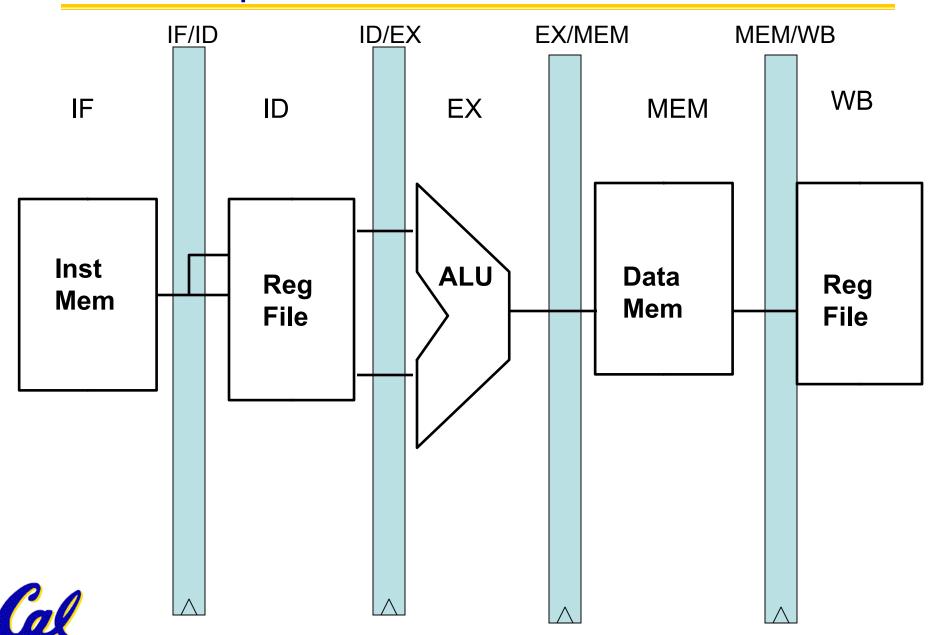

## A Pipelined Processor

CS 152 Lab Lecture (2) Fall 2003 © UCB

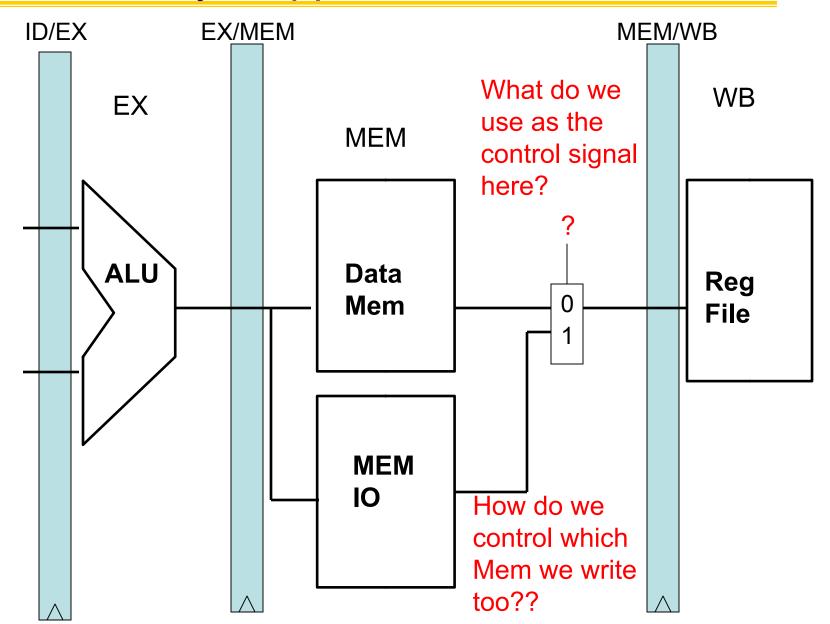

## Memory-Mapped IO

- Any store or writes to memory when the top address bit is 1 will write to your Memory-Mapped IO rather than normal memory.

- Allows us to display information to HEX LEDs using SW

- Allows us to take input from the board using LW

- During simulation, the I/O space is simulated by using text files.

CS 152 Lab Lecture (3)

## Memory-Mapped IO

Cal

CS 152 Lab Lecture (4) Fall 2003 © UCB

## Memory-Mapped IO

- Internally, there are only 2 registers.

- The only two valid addresses you can write to are 0xFFFFFF0 and 0xFFFFFF4.

- Note that 0xFFFFFF4 is -12....

- Other writes to memio can be ignored.

- You may want to make use of the Verilog syntax:

- `ifdef synthesis, `else, `endif

Fall 2003 © UCB

## Adding the Multiplier

- The multiplier is a "coprocessor"

- It executes on its own, and the processor doesn't stall unless it gets another multu, mfhi, or mflo.

- What signal do we need to add to allow the processor to stall?

- What stage do we send the signals to the multiplier?

CS 152 Lab Lecture (6) Fall 2003 © UCB

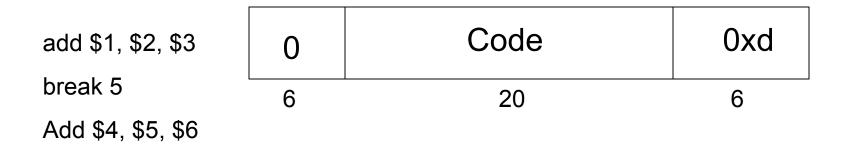

#### The Break Instruction

- The number following the break instruction (in this case 5), is placed into the Code segment of the instruction.

- You need to display the lower 7 bits of these numbers as part of the STAT signal during a break.

- Your processor should stall until it receives an external signal called "release." Release is a debounced input from the board. What about simulation??

CS 152 Lab Lecture (7) Fall 2003 © UCB

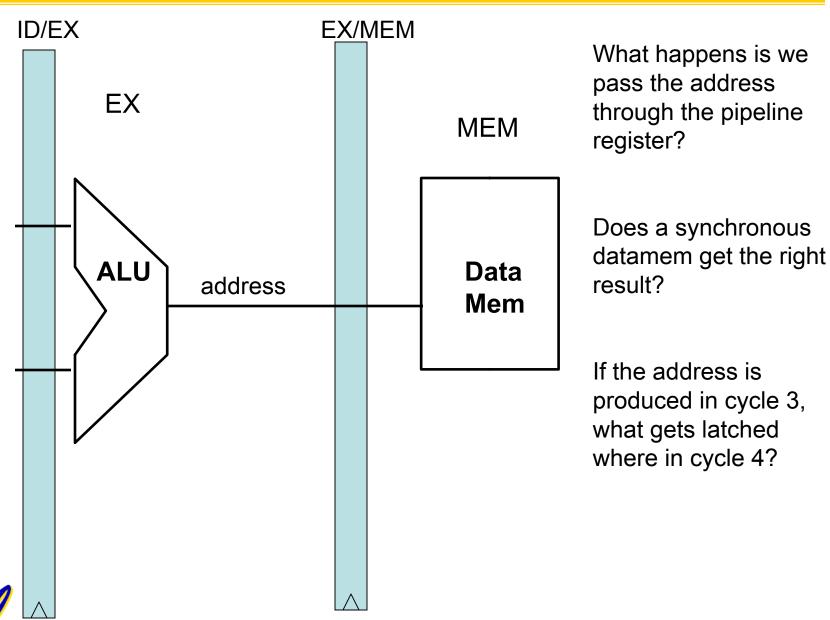

## Synchronous Memory

- This lab uses synchronous memory.

- Synchronous writes—just like last time

- Synchronous reads—NOT LIKE LAST

TIME

- Address/control inputs to your memory have to be ready <u>before</u> the posedge of the cycle you want the results!

- Why can't we use synchronous reads in the single-cycle processor?

CS 152 Lab Lecture (8) Fall 2003 © UCB

# Synchronous Memory

CS 152 Lab Lecture (9) Fall 2003 © UCB

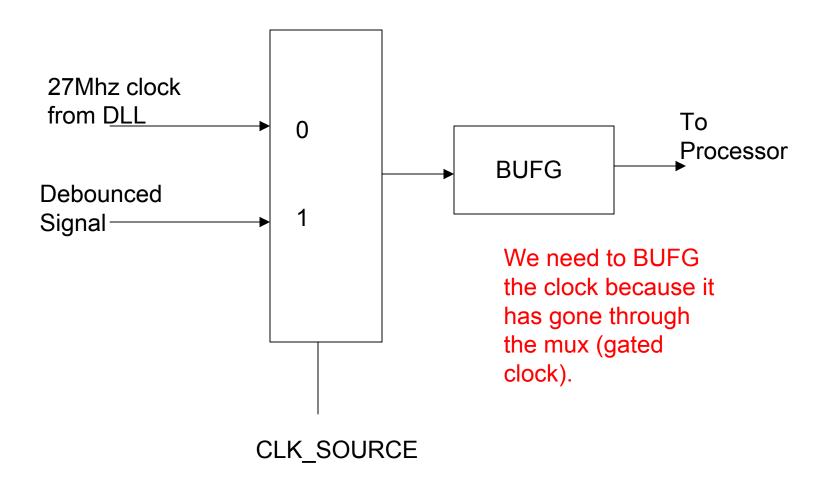

## Single Stepped Clock

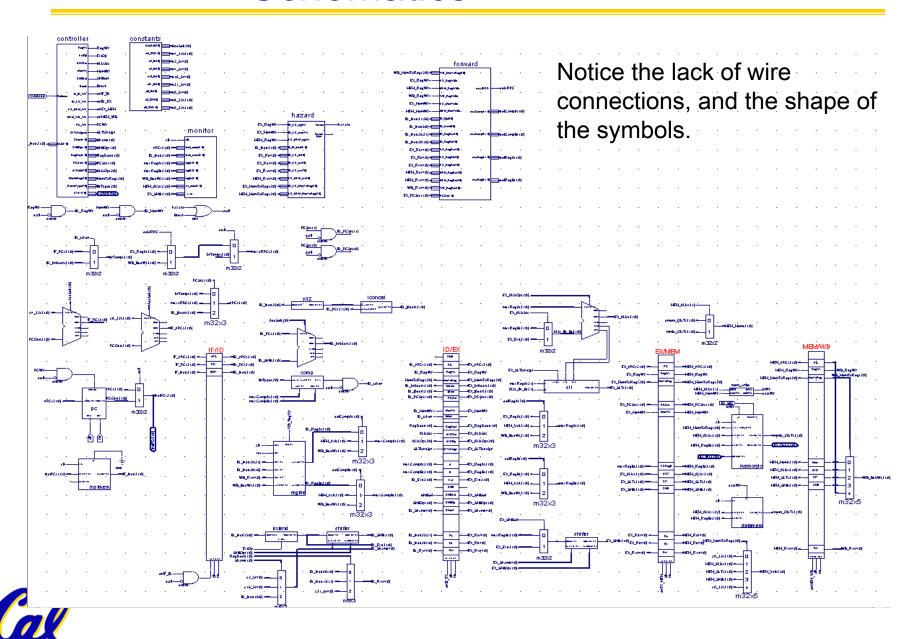

## **Schematics**

CS 152 Lab Lecture (11) Fall 2003 © UCB

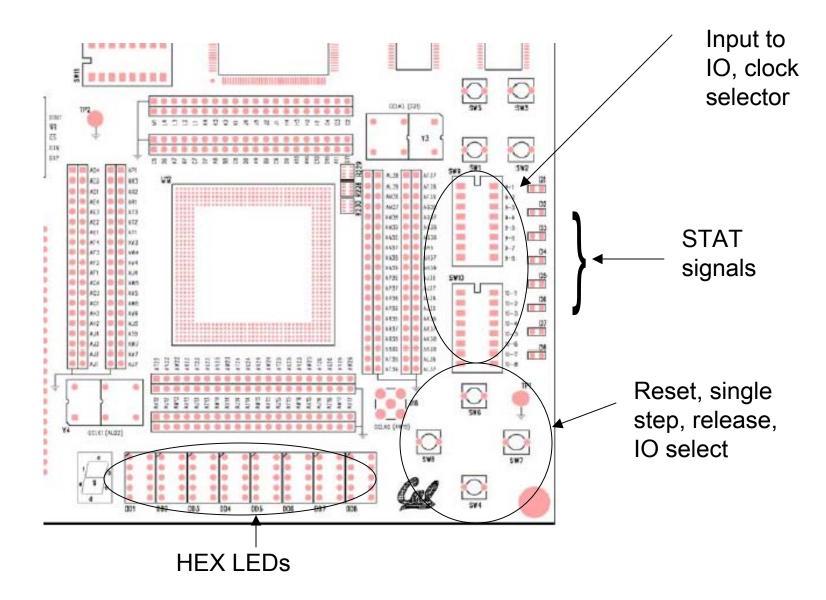

## **Board Connections**

CS 152 Lab Lecture (12) Fall 2003 © UCB