### CS152 – Computer Architecture and Engineering Lecture 20 – TLB/Virtual memory

2003-11-04

Dave Patterson

(www.cs.berkeley.edu/~patterson)

www-inst.eecs.berkeley.edu/~cs152/

atterson Fall 200

### Review

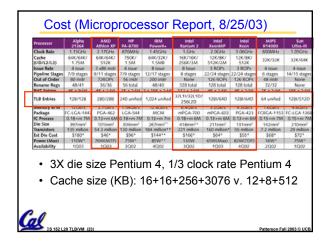

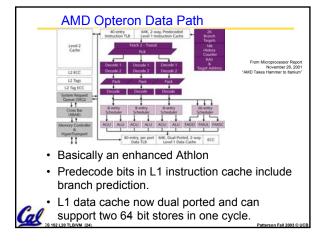

### IA 32000 processors

- HW translation to RISC operations

- Superpipelined P4 with 22-24 stages vs. 12 stage Opteron

- Trace cache in P4

- SSE2 increasing floating point performance

- Very Long Instruction Word machines (VLIW)

- ⇒ Multiple operations coded in single, long instruction

- EPIC as a hybrid between VLIW and traditional pipelined computers

- Uses many more registers

- 64 bit: New ISA (IA 64) or Evolution (AMD64)?

- 64-bit Address space needed larger DRAM memory

Patterson Fall 2003 © UCI

### 61C Review- Three Advantages of Virtual Memory

### 1) Translation:

- Program can be given consistent view of memory, even though physical memory is scrambled

- Makes multiple processes reasonable

- Only the most important part of program ("Working Set") must be in physical memory

- Contiguous structures (like stacks) use only as much physical memory as necessary yet still grow later

Patterson Fall 2003 © UCB

### 61C Review- Three Advantages of Virtual Memory

### 2) Protection:

- Different processes protected from each other

- Different pages can be given special behavior

- Read Only, No execute, Invisible to user programs,...

- Kernel data protected from User programs

- Very important for protection from malicious programs ⇒ Far more "viruses" under Microsoft Windows

- Special Mode in processor ("Kernel more") allows processor to change page table/TLB

### 3) Sharing:

Can map same physical page to multiple users ("Shared memory")

Patterson Fall 2003

# What is the size of information blocks that are transferred from secondary to main storage (M)? ⇒ page size (Contrast with physical block size on disk, l.e. sector size) Which region of M is to hold the new block ⇒ placement policy How do we find a page when we look for it? ⇒ block identification

Issues in Virtual Memory System Design

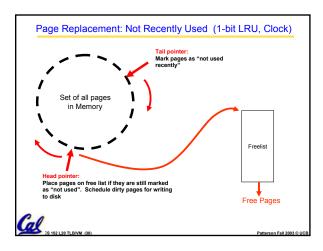

Block of information brought into M, and M is full, then some region of M must be released to make room for the new block ⇒ replacement policy

What do we do on a write? ⇒ write policy

Missing item fetched from secondary memory only on the occurrence of a fault ⇒ demand load policy

Patterson Fall 2003 © UCB

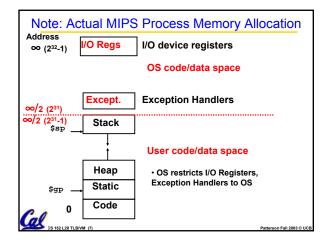

### Kernel/User Mode

- Generally restrict device access, page table to OS

- · HOW?

- Add a "mode bit" to the machine: K/U

- Only allow SW in "kernel mode" to access device registers, page table

- If user programs could access I/O devices and page tables directly?

- could destroy each others data, ...

- might break the devices, ...

Patterson Fall 2003 © UCE

### MIPS Syscall

- · How does user invoke the OS?

- syscall instruction: invoke the kernel (Go to 0x80000080, change to kernel mode)

- By software convention, \$v0 has system service requested: OS performs request

### Instruction Set Support for VM/OS

- How to prevent user program from changing page tables and go anywhere?

- -Bit in Status Register determines whether in user mode or OS (kernel) mode:

Kernel/User bit (KU) (0  $\Rightarrow$  kernel, 1  $\Rightarrow$  user)

Assume Unused KU IE

Status Register

- -On exception/interrupt disable interrupts (IE=0) and go into kernel mode (KU=0)

- Only change the page table when in kernel mode (Operating System)

atterson Fall 20

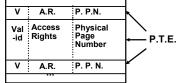

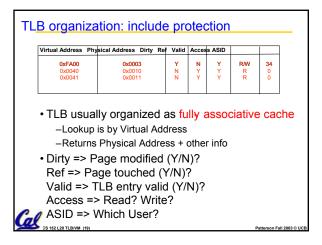

### 61C Review- Page Table Entry (PTE) Format

- Contains either Physical Page Number or indication not in Main Memory

- OS maps to disk if Not Valid (V = 0)

Page Table

If valid, also check if have permission to use page: <u>Access Rights</u> (A.R.) may be Read Only, Read/Write, Executable

### 61C Review- Comparing the 2 levels of hierarchy

Cache Version Virtual Memory vers.

Block or Line Page

Miss Page Fault

Block Size: 32-64B Page Size: 4K-8KB Placement: Fully Associative

Direct Mapped.

N-way Set Associative

Replacement: Least Recently Used

LRU or Random (LRU)

Write Thru or Back Write Back

Patterson Fall 2003 © UCB

### 61C Review- Notes on Page Table

- Solves Fragmentation problem: all chunks same size, so all holes can be used

- OS must reserve "<u>Swap Space</u>" on disk for each process

- To grow a process, ask Operating System

- If unused pages, OS uses them first

- If not, OS swaps some old pages to disk

- (Least Recently Used to pick pages to swap)

- · Each process has own Page Table

Patterson Fall 2003 © UC

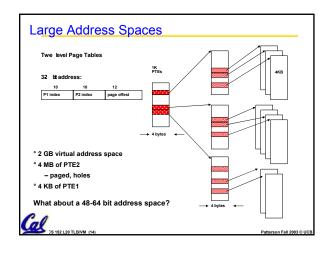

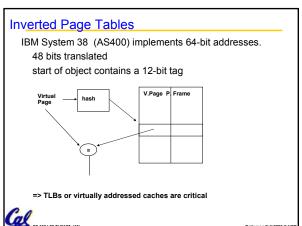

## How big is the translation (page) table? Virtual Page Number · Simplest way to implement "fully associative" lookup policy is with large lookup table. · Each entry in table is some number of bytes, say • With 4K pages, 32 bit address space, need: $2^{32}/4K = 2^{20} = 1$ Meg entries x 4 bytes = 4MB • With 4K pages, 64 bit address space, need: $2^{64}/4K = 2^{52}$ entries = BIG! · Can't keep whole page table in memory!

### Administrivia

- 8 more PCs in 125 Cory, 3 more boards

- Thur 11/6: Design Doc for Final Project due - Deep pipeline? Superscalar? Out of order?

- Tue 11/11: Veteran's Day (no lecture)

- Fri 11/14: Demo Project modules

- Wed 11/19: 5:30 PM Midterm 2 in 1 LeConte - No lecture Thu 11/20 due to evening midterm

- Tues 11/22: Field trip to Xilinx

- CS 152 Project Week: 12/1 to 12/5

- Mon: TA Project demo, Tue: 30 min Presentation, Wed: Processor racing, Fri: Written report

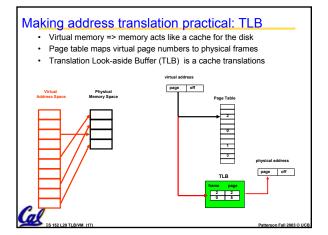

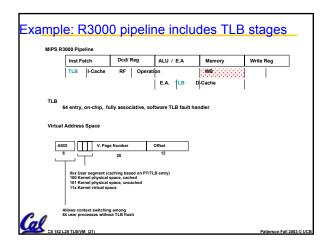

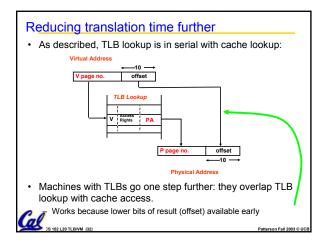

### Why Translation Lookaside Buffer (TLB)?

- Paging is most popular implementation of virtual memory (vs. base/bounds)

- · Every paged virtual memory access must be checked against Entry of Page Table in memory to provide protection

- Cache of Page Table Entries (TLB) makes address translation possible without memory access in common case to make fast

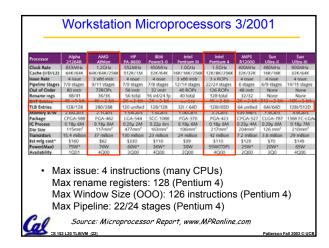

### TLB/VM in P4 vs. Opteron

Intel Pentium P4

AMD Opteron

Virtual address 32 bits 48 bits Physical address 36 bits 40 bits 4 KB, 2/4 MB Page size 4 KB. 2/4 MB

Intel:

- · 1 TLB for instructions and 1 TLB for data

- Both are 4-way set associative

- Both use Pseudo-LRU replacement

- Both have 128 entries

- TLB misses handled in hardware

- · 2 TLBs for instructions and 2 TLBs for data

- Both L1 TLBs Fully associative, LRU replacement

- Both L2 TLB 4-way set associativity, Pseudo-LRU

- Both L1 TLBs have 40 entries

- Both L2 TLB have 512 entries

- De misses handled in hardware

### **Peer Instruction**

Why do stack buffer overflow attacks work on Microsoft OS running on IA-32?

- 1) Code and data are interchangable

- 2) Bugs in MS operating system

- 3) Lack of No Execute Page Protection in IA-32

1.ABC: FFF 5. ABC: TFF 2.ABC: FFT 6. ABC: TFT 3.ABC: FTF 7. ABC: TTF 4.ABC: FTT 8. ABC: TTT

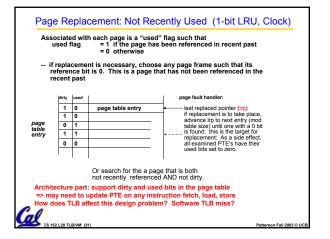

### What is the replacement policy for TLBs?

- On a TLB miss, we check the page table for an entry. Two architectural possibilities:

- Hardware "table-walk" (Sparc, among others)

- · Structure of page table must be known to hardware

- Software "table-walk" (MIPS was one of the first)

- · Lots of flexibility

- Can be expensive with modern operating systems.

- What if missing Entry is not in page table?

- This is called a "Page Fault"

⇒ requested virtual page is not in memory

- Operating system must take over (CS162)

- pick a page to discard (possibly writing it to disk)

- start loading the page in from disk · schedule some other process to run

- Note: possible that parts of page table are not even in memory (I.e. paged out!)

- The root of the page table always "pegged" in memory

### **MIPS Control Registers**

Register CP0 Description register

number

- EPC 14 Where to restart after exception

- Cause 13 Cause of exception

- BadVAddr 8 Address that caused exception

- Index Location in TLB to be read or written

- Random Pseudo- random location in TLB

- EntryLo Physical page address and flags

- EntryHi 10 Virtual page address

- Page Table Address and Page Context Number

### MIPS TLB Handler

mfc0 \$k1,Context # copy address of PTE into temp \$k1 \$k1, 0(\$k1) # put PTE into temp \$k1

mtc0 \$k1,EntryLo # put PTE into special register EntryLo tlbwr # put EntryLo into TLB entry at Random # return from TLB miss exception eret

- •The exception transfers to address 8000 0000<sub>hex</sub>, the location of the TLB miss handler

- Random implements random replacement, so it is basically a free running counter.

- •A TLB miss takes about a dozen clock cycles

### **VM Performance**

- VM invented to enable a small memory to act as a large one but ...

- Performance difference disk and memory =>a program routinely accesses more virtual memory than it has physical memory it will run very slowly.

- continuously swapping pages between memory and disk, called thrashing.

- Easiest solution is to buy more memory

- Or re-examine algorithm and data structures to see if reduce working set.

S 152 L20 TLB/VM (39) Patterson Fall 2003 © UI

### **TLB Performance**

- · Common performance problem: TLB misses.

- TLB 32 to 64 => a program could easily see a high TLB miss rate since < 256 KB</li>

- Most ISAs now support variable page sizes

- MIPS supports 4 KB, 16 KB, 64 KB, 256 KB, 1

MB, 4 MB, 16 MB, 64, MB, and 256 MB pages.

- Practical challenge getting OS to allow programs to select these larger page sizes

- Complex solution is to re-examine the algorithm and data structures to reduce the working set of pages

S 152 | 20 TI BAM (40)

Patterson Fall 2003 © U

### Summary #1 / 2 Things to Remember

- Virtual memory to Physical Memory Translation too slow?

- Add a cache of Virtual to Physical Address Translations, called a TLB

- Need more compact representation to reduce memory size cost of simple 1 level page table (especially 32 ⇒ 64 tit address)

- Spatial Locality means Working Set of Pages is all that must be in memory for process to run fairly well

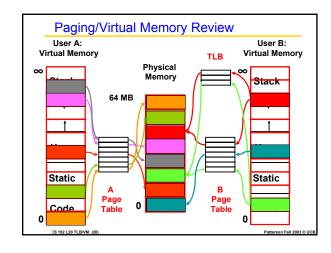

- Virtual Memory allows protected sharing of memory between processes with less

swapping to disk

CS 152 L20 TLB/VM (41)

Patterson Fall 2003 © III

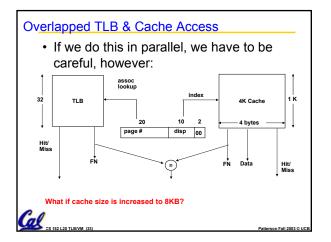

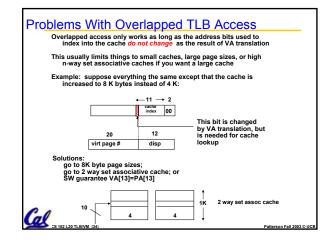

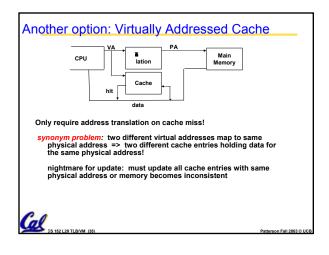

### Summary #2 / 2: TLB/Virtual Memory

- VM allows many processes to share single memory without having to swap all processes to disk

- Translation, Protection, and Sharing are more important than memory hierarchy

- Page tables map virtual address to physical address

- TLBs are a cache on translation and are extremely important for good performance

- Special tricks necessary to keep TLB out of critical cacheaccess path

- TLB misses are significant in processor performance:

- These are funny times: most systems can't access all of 2nd level cache without TLB misses!

S 152 L20 TLB/VM (42)

Patterson Fall 2003 © UC