# CS152 – Computer Architecture and Engineering

**Lecture 4 – Overview of Logic Design**

2003-09-04

Dave Patterson (www.cs.berkeley.edu/~patterson)

www-inst.eecs.berkeley.edu/~cs152/

### **Review**

- 4-LUT FPGAs are basically interconnect plus distributed RAM that can be programmed to act as any logical function of 4 inputs

- CAD tools do the partitioning, routing, and placement functions onto CLBs

- FPGAs offer compromise of performance, Non Recurring Engineering, unit cost, time to market vs. ASICs or microprocessors (plus software)

|                     | <b>Performance</b> | NRE   | <b>Unit Cost</b> | TTM   |

|---------------------|--------------------|-------|------------------|-------|

| Better <sup>4</sup> | ASIC               | MICRO | ASIC             | MICRO |

|                     | FPGA               | FPGA  | MICRO            | FPGA  |

| Worse               | MICRO              | ASIC  | FPGA             | ASIC  |

CS 152 L04 Logic (2) Patterson Fall 2003 © UCB

### **Outline**

- °Critical Path

- °Setup / Hold Times

- °Clock skew

- ° Finite State Machines

- °One-hot encoding

- ° DeMorgan's Theorem

- ° Don't cares/ Karnaugh Maps

- °IC costs

CS 152 L04 Logic (3) Patterson Fall 2003 © UCB

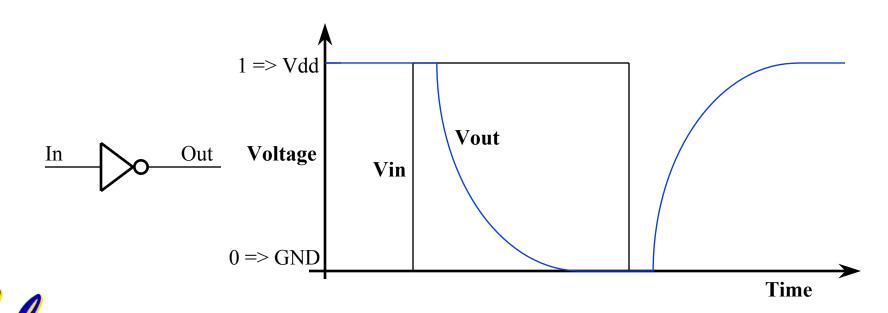

# **Ideal versus Reality**

- ° When input 0 -> 1, output 1 -> 0 but NOT instantly

- Output goes 1 -> 0: output voltage goes from Vdd (5v) to 0v

- ° When input 1 -> 0, output 0 -> 1 but NOT instantly

- Output goes 0 -> 1: output voltage goes from 0v to Vdd (5v)

- ° Voltage does not like to change instantaneously

CS 152 L04 Logic (4) Patterson Fall 2003 © UCB

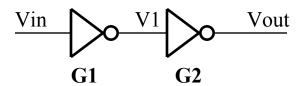

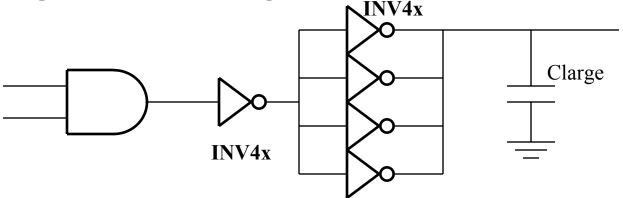

### **Series Connection**

- ° Total Propagation Delay = Sum of individual delays = d1 + d2

- ° Capacitance C1 has two components:

- Capacitance of the wire connecting the two gates

Input capacitance of the second inverter

CS 152 L04 Logic (5) Patterson Fall 2003 © UCB

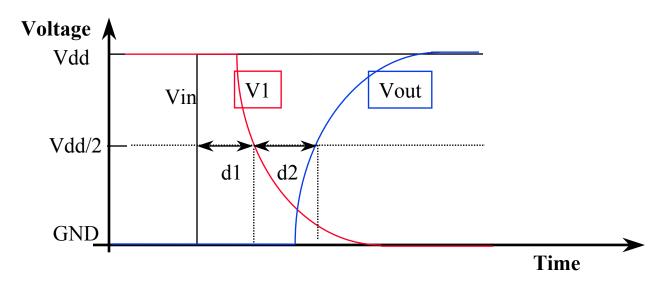

# Calculating Aggregate Delays; Critcal Path

- ° Sum delays along serial paths

- ° Delay (Vin -> V2) ! = Delay (Vin -> V3)

- Delay (Vin -> V2) = Delay (Vin -> V1) + Delay (V1 -> V2)

- Delay (Vin -> V3) = Delay (Vin -> V1) + Delay (V1 -> V3)

- ° Capacitance₁ = Wire Capacitance + Capacitance<sub>in</sub> of Invertor<sub>2</sub> + Capacitance<sub>in</sub> of Invertor<sub>3</sub>

° Critical Path = The longest among the N parallel paths

Patterson Fall 2003 © UCB

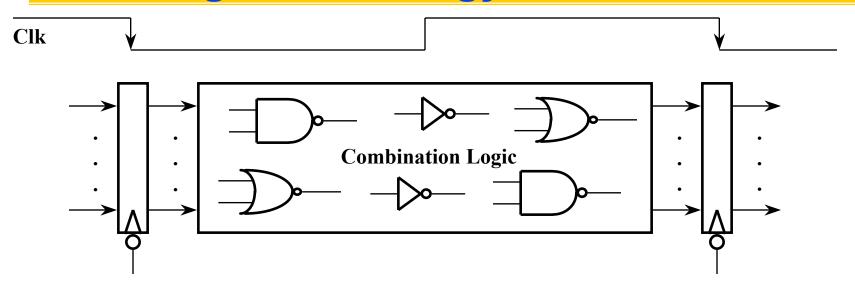

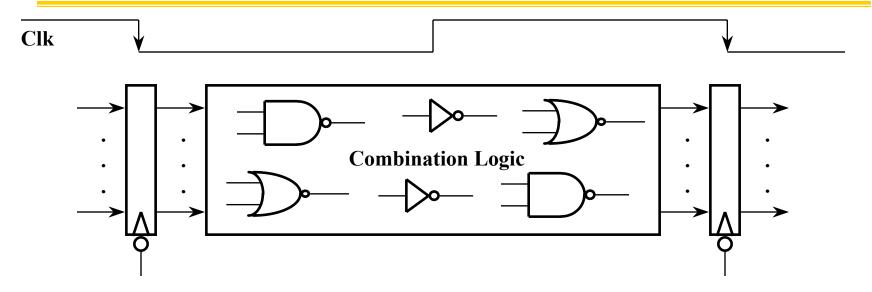

# **Clocking Methodology**

- ° All storage elements are clocked by the same clock edge

- ° The combination logic block's:

- Inputs are updated at each clock tick

- All outputs MUST be stable before the next clock tick

CS 152 L04 Logic (7) Patterson Fall 2003 © UCB

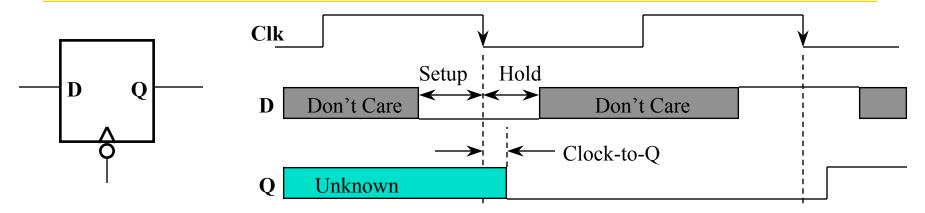

# **Storage Element's Timing Model**

- Setup Time: Input must be stable BEFORE trigger clock edge

- Our Property of the second of the second

- ° Clock-to-Q time:

- Output cannot change instantaneously at the trigger clock edge

- Similar to delay in logic gates, two components:

- Internal Clock-to-Q

- Load dependent Clock-to-Q

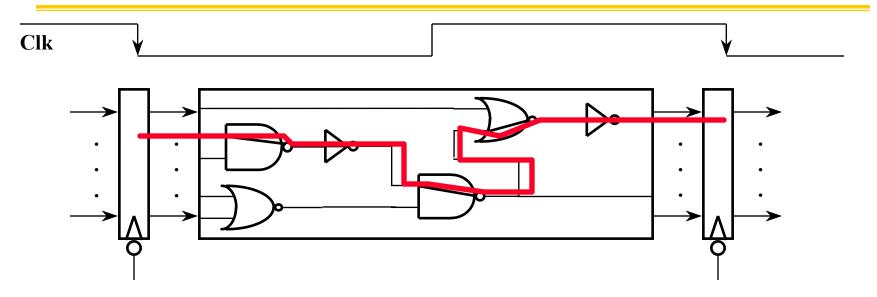

### **Critical Path & Cycle Time**

- ° Critical path: the slowest path between any two storage devices

- ° Cycle time is a function of the critical path

- ° must be greater than:

Clock-to-Q + Longest Path through, Combination Logic + Setup

Patterson Fall 2003 © UCB

### **Tricks to Reduce Cycle Time**

° Reduce the number of gate levels

- Pay attention to loading

- ° One gate driving many gates is a bad idea

- ° Avoid using a small gate to drive a long wire

- ° Use multiple stages to drive large load

CS 152 L04 Logic (10)

Patterson Fall 2003 © UCB

# Administrivia (1/2)

- Even though there is lots of space in the class, there is a mistake in Telebears that is preventing us from adding people into sections. Therefore, if you are not enrolled in the course, but want to get in, here is what you have to do:

- °By Friday 9/5 1:00pm, talk to Michael David Sasson (in person) in 379 Soda

- °Be sure to tell him which section you want to move into. If you don't talk to him by Friday, we can't add you to the class!

# Administrivia (2/2)

- °Friday 9/5 lab demo in 125 Cory 3-4

- If didn't take CS 150, should go to demo

- Office hours in Lab

- Mon 5 6:30 Jack, Tue 3:30-5 Kurt,

Wed 3 4:30 John

- ° Dave's office hours Tue 3:30 5

- °HW #1 Due Wed 9/10

- °Lab #2 done in pairs since 15 FPGA boards, 33 PCs. Due Monday 9/15

Form 4 or 5 person teams by Friday 9/12

CS 152 L04 Logic (12) Patterson Fall 2003 © UCB

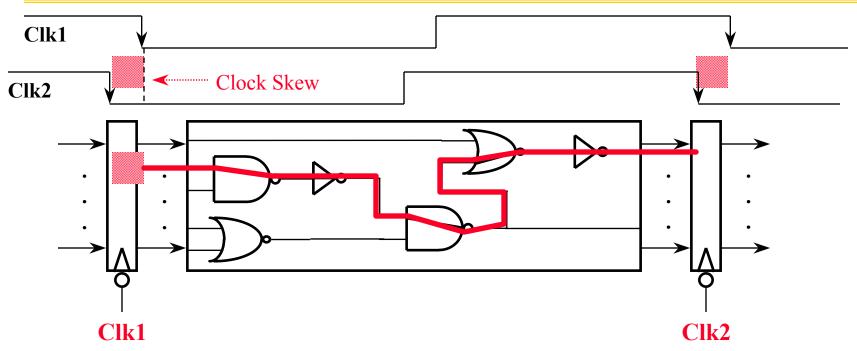

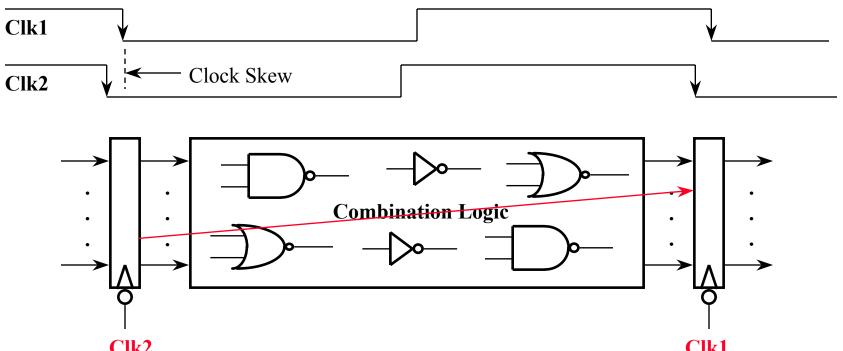

# **Clock Skew's Effect on Cycle Time**

- ° The worst case scenario for cycle time consideration:

- The input register sees CLK1

- The output register sees CLK2

- ° Cycle Time Clock Skew ≥ CLK-to-Q + Longest Delay + Setup ⇒ Cycle Time ≥ CLK-to-Q + Longest Delay + Setup + Clock Skew

### **How to Avoid Hold Time Violation?**

- ° Hold time requirement:

- Input to register must NOT change immediately after the clock tick

- This is usually easy to meet in the "edge trigger" clocking scheme

- ° CLK-to-Q + Shortest Delay Path must be greater than Hold Time

### **Clock Skew's Effect on Hold Time**

- The worst case scenario for hold time consideration:

- The input register sees CLK2

- The output register sees CLK1

- fast FF2 output must not change input to FF1 for same clock edge

- ° (CLK-to-Q + Shortest Delay Path Clock Skew) > Hold **▼**Time

- Danger is one fast path (e.g., 1 gate) violate hold time

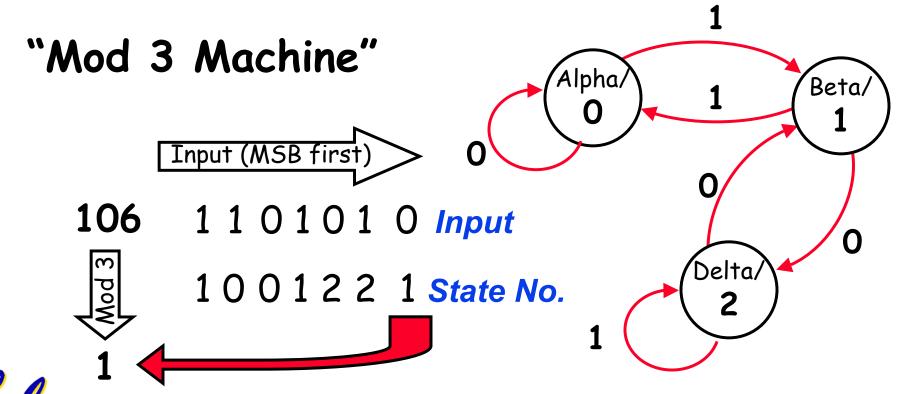

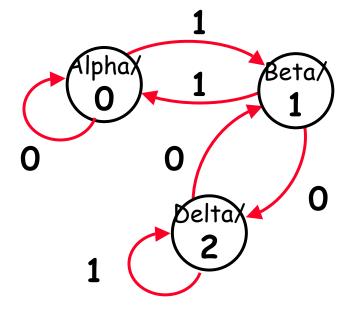

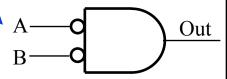

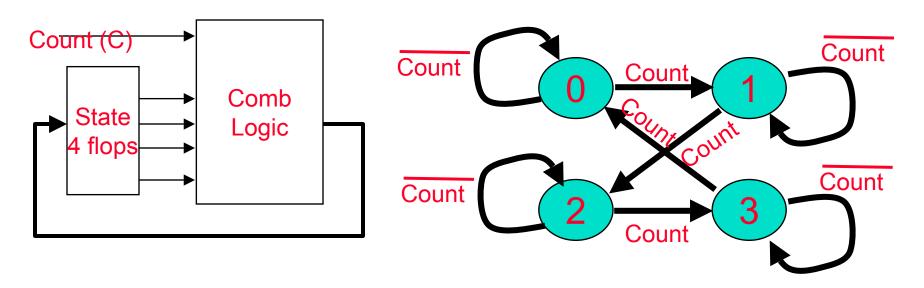

### **Finite State Machines:**

- ° System state is explicit in representation

- ° Transitions between states represented as arrows with inputs on arcs.

- ° Output may be either part of state or on arcs

CS 152 L04 Logic (16) Patterson Fall 2003 © UCB

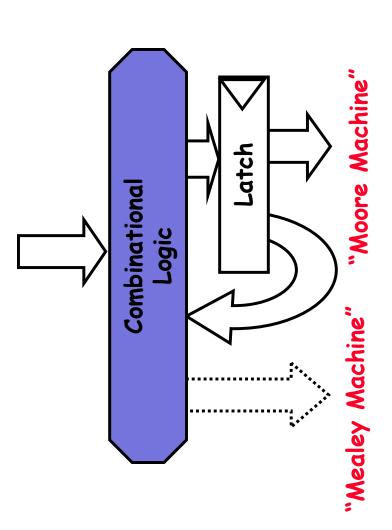

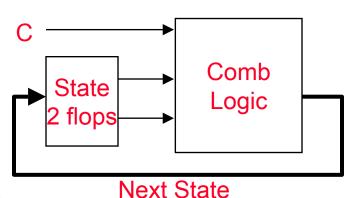

### **FSM Implementation as Combinational logic + Latch**

| Input | Stateold | Statenew |

|-------|----------|----------|

| 0     | 00       | 00       |

| 0     | 01       | 10       |

| 0     | 10       | 01       |

| 1     | 00       | 01       |

| 1     | 01       | 00       |

| 1     | 10       | 10       |

CS 152 L04 Logic (17) Patterson Fall 2003 © UCB

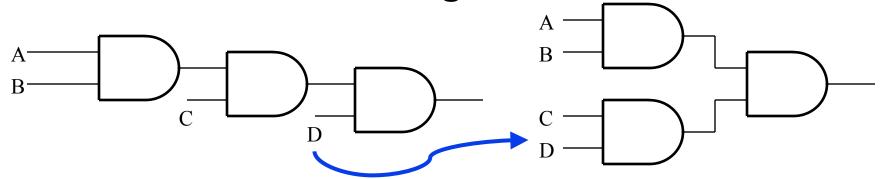

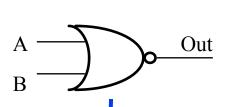

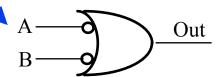

### DeMorgan's theorem: Push Bubbles and Morph

#### **NAND Gate**

| A | В | Out |

|---|---|-----|

| 0 | 0 | 1   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 0   |

#### **NOR Gate**

| A | B | Out |

|---|---|-----|

| 0 | 0 | 1   |

| 0 | 1 | 0   |

| 1 | 0 | 0   |

| 1 | 1 | 0   |

•Complement operands, or=>and, and=>or

Out =

$$\overline{A \cdot B} = \overline{A} + \overline{B}$$

| A | В | Ā | B | Out |

|---|---|---|---|-----|

| 0 | 0 | 1 | 1 | 1   |

| 0 | 1 | 1 | 0 | 1   |

| 1 | 0 | 0 | 1 | 1   |

| 1 | 1 | 0 | 0 | 0   |

Out =

$$\overline{A + B} = \overline{A} \cdot \overline{B}$$

|           | A | B | Ā | $\overline{\mathbf{B}}$ | Out |

|-----------|---|---|---|-------------------------|-----|

| <u>t_</u> | 0 | 0 | 1 | 1                       | 1   |

|           | 0 | 1 | 1 | 0                       | 0   |

|           | 1 | 0 | 0 | 1                       | 0   |

|           | 1 | 1 | 0 | 0                       | 0   |

CS 152 L04 Logic (18) Patterson Fall 2003 © UCB

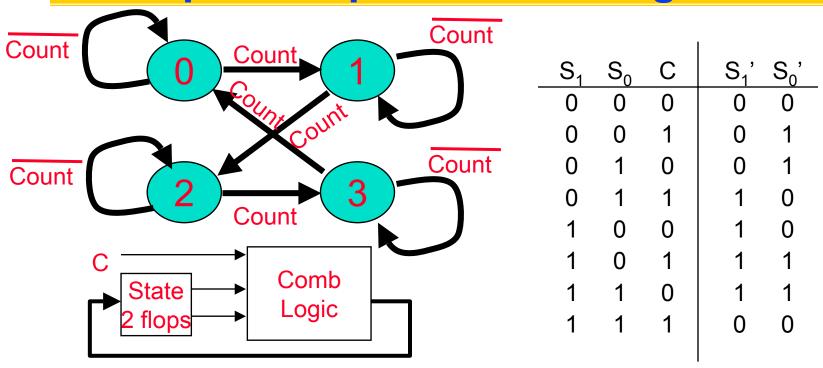

### **Example: Simplification of logic**

$$\begin{split} \boldsymbol{S}_{0}' &= \left(\overline{\boldsymbol{S}_{1}} \cdot \overline{\boldsymbol{S}_{0}} \cdot \boldsymbol{C}\right) + \left(\overline{\boldsymbol{S}_{1}} \cdot \boldsymbol{S}_{0} \cdot \overline{\boldsymbol{C}}\right) + \left(\boldsymbol{S}_{1} \cdot \overline{\boldsymbol{S}_{0}} \cdot \boldsymbol{C}\right) + \left(\boldsymbol{S}_{1} \cdot \boldsymbol{S}_{0} \cdot \overline{\boldsymbol{C}}\right) \\ &= \left(\overline{\boldsymbol{S}_{0}} \cdot \boldsymbol{C}\right) + \left(\boldsymbol{S}_{0} \cdot \overline{\boldsymbol{C}}\right) \end{split}$$

$$\mathbf{S}_{1}' = \left(\overline{\mathbf{S}_{1}} \cdot \mathbf{S}_{0} \cdot \mathbf{C}\right) + \left(\mathbf{S}_{1} \cdot \overline{\mathbf{S}_{0}} \cdot \overline{\mathbf{C}}\right) + \left(\mathbf{S}_{1} \cdot \overline{\mathbf{S}_{0}} \cdot \mathbf{C}\right) + \left(\mathbf{S}_{1} \cdot \mathbf{S}_{0} \cdot \overline{\mathbf{C}}\right)$$

$$= \left(\overline{\mathbf{S}_{1}} \cdot \mathbf{S}_{0} \cdot \mathbf{C}\right) + \left(\mathbf{S}_{1} \cdot \overline{\mathbf{C}}\right) + \left(\mathbf{S}_{1} \cdot \overline{\mathbf{S}_{0}}\right)$$

CS 152 L04 Logic (19) Patterson Fall 2003 © UCB

### Karnaugh Map for easier simplification

### Group Ones in powers of 2, simplify, OR-together

| $S_1$ | $S_0$ | С | $S_1$ , $S_0$ |   |

|-------|-------|---|---------------|---|

| 0     | 0     | 0 | 0 0           | _ |

| 0     | 0     | 1 | 0 1           |   |

| 0     | 1     | 0 | 0 1           |   |

| 0     | 1     | 1 | 1 0           |   |

| 1     | 0     | 0 | 1 0           |   |

| 1     | 0     | 1 | 1 1           |   |

| 1     | 1     | 0 | 1 1           |   |

| 1     | 1     | 1 | 0 0           |   |

$$\mathbf{S}_{\mathbf{0}}' = \left(\overline{\mathbf{S}_{\mathbf{0}}} \cdot \mathbf{C}\right) + \left(\mathbf{S}_{\mathbf{0}} \cdot \overline{\mathbf{C}}\right)$$

$$\mathbf{S}_{1}' = \left(\overline{\mathbf{S}_{1}} \cdot \mathbf{S}_{0} \cdot \mathbf{C}\right) + \left(\mathbf{S}_{1} \cdot \overline{\mathbf{C}}\right) + \left(\mathbf{S}_{1} \cdot \overline{\mathbf{S}_{0}}\right)$$

CS 152 L04 Logic (20) Patterson Fall 2003 © UCB

# "One-Hot Encoding": 1 FF/state vs. log<sub>2</sub> FFs

- One Flip-flop per stateno decode HW of state no.

- ° Only one state bit = 1 at a time

- Much faster combinational logic

- ° Tradeoff: Size ⇔Speed

$$\boldsymbol{S}_{\mathbf{0}}' = \left(\boldsymbol{S}_{\mathbf{0}} \cdot \overline{\boldsymbol{C}}\right) + \left(\boldsymbol{S}_{\mathbf{3}} \cdot \boldsymbol{C}\right)$$

$$\boldsymbol{S}_{1}' = \left(\boldsymbol{S}_{1} \cdot \overline{\boldsymbol{C}}\right) + \left(\boldsymbol{S}_{0} \cdot \boldsymbol{C}\right)$$

$$\mathbf{S}_{\mathbf{2}}' = \left(\mathbf{S}_{\mathbf{2}} \cdot \overline{\mathbf{C}}\right) + \left(\mathbf{S}_{\mathbf{1}} \cdot \mathbf{C}\right)$$

$$\mathbf{S_3'} = \left(\mathbf{S_3} \cdot \overline{\mathbf{C}}\right) + \left(\mathbf{S_2} \cdot \mathbf{C}\right)$$

CS 152 L04 Logic (21)

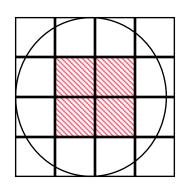

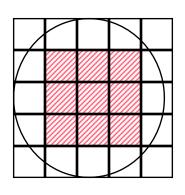

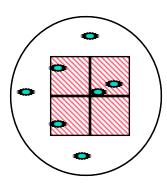

### **Integrated Circuit Costs**

Dies per wafer =

$$\frac{\pi * (Wafer\_diam / 2)^2}{Die Area}$$

-  $\frac{\pi * Wafer\_diam}{\sqrt{2 * Die Area}}$  - Test dies  $\approx \frac{Wafer Area}{Die Area}$

$$\left\{ 1 + \frac{\text{Defects\_per\_unit\_area * Die\_Area}}{\alpha} \right\}^{\alpha}$$

Die Cost is roughly polynomial with die size: (die area)<sup>3</sup> or (die area)<sup>4</sup>

<sup>▶</sup> CS 152 L04 Logic (22) Patterson Fall 2003 © UCB

# Real World Examples: 2003

| Feature                | Broadcom<br>BCM1250                                                | IBM 440GX                                                  | Intrinsity<br>FastMATH                         | Motorola<br>MPC7447 | Motorola<br>MPC8560                                               | NEC<br>VR7701           | PMC<br>RM9000x2GL                                                      | Toshiba<br>4955CFG          |

|------------------------|--------------------------------------------------------------------|------------------------------------------------------------|------------------------------------------------|---------------------|-------------------------------------------------------------------|-------------------------|------------------------------------------------------------------------|-----------------------------|

| Architecture           | Enhanced<br>MIPS64                                                 | PowerPC:<br>Book E                                         | MIPS                                           | PPC G4+             | e500<br>PowerPC                                                   | MIPS IV +<br>extensions | Enhanced<br>MIPS64                                                     | MIPS III*                   |

| Core Freq (MHz)        | 600-800                                                            | 500-800                                                    | 2GHz                                           | 1.3GHz              | 833                                                               | 400                     | 1,000                                                                  | 400                         |

| Bus Freq (MHz)         | 200                                                                | 166                                                        | 200                                            | 167                 | 166                                                               | 200 (DDR)               | 200                                                                    | 133                         |

| Cache (I/D)            | 32K/32K                                                            | 32K/32K                                                    | 16K/16K                                        | 32K/32K             | 32K/32K                                                           | 32K/32K                 | 32K/32K                                                                | 32K/32K                     |

| Level 2 Cache          | 512K                                                               | 256K                                                       | 1M                                             | 512K                | 256K                                                              | 256K                    | 512K                                                                   | No                          |

| FPU                    | Yes                                                                | No                                                         | No                                             | Yes                 | Yes                                                               | Yes                     | Yes                                                                    | Yes                         |

| Pipeline Stages        | 8-9                                                                | 7                                                          | 8-12                                           | 7                   | 7                                                                 | 10                      | 7                                                                      | 5                           |

| Instructions per Clock | 4                                                                  | 2                                                          | 1                                              | 3+branch            | 3+branch                                                          | 2                       | 2                                                                      | 1                           |

| Special Features       | Dual core,<br>Hyper-<br>Transport,<br>10/100/<br>1,000<br>Ethernet | 10/100/1,000<br>Ethernet; TCP/IP<br>acceleration,<br>PCI-X | RapidIO,<br>SIMD 4x4<br>matrix/<br>vector unit | AltiVec             | RapidIO,<br>2×10/100/<br>1,000<br>Ethernet,<br>PCI-X, DDR,<br>CPM | Out of order execution  | Dual core,<br>Hyper-<br>Transport, 3<br>10/100/1,000<br>Ethernet ports | One of first<br>90nm chips. |

| Voltage (core)         | 1.2                                                                | 1.5                                                        | 1                                              | 1.3                 | 1.2                                                               | 1.5                     | 1.2                                                                    | 1.2                         |

| Power (typ)            | 10W                                                                | 4.5W@533MHz                                                | 13.5W                                          | 7.5W@1GHz           | 9W @833MHz                                                        | 4W                      | 12W                                                                    | 0.6W                        |

| Transistors (millions) | ~60                                                                | DTP                                                        | 68M                                            | 58                  | DTP                                                               | 6.5                     | 50                                                                     | 5                           |

| IC Process             | 0.13µm                                                             | 0.13µm                                                     | 0.13µm                                         | 0.13µm SOI          | 0.13µm                                                            | 0.15µm                  | 0.13µm copper                                                          | 90nm                        |

| Die Size (mm²)         | DTP                                                                | DTP                                                        | 122                                            | 98                  | DTP                                                               | DTP                     | 128.2                                                                  | 20.83                       |

| Availability           | Now                                                                | Sampling                                                   | Sampling                                       | ES: Now<br>MP: 4Q03 | Sampling now                                                      | Sampling                | Sampling                                                               | Sampling<br>11/03           |

| Price (10K)            | \$499                                                              | \$71 (500MHz)                                              | \$349                                          | \$189               | \$125                                                             | \$90                    | \$379                                                                  | \$22                        |

DTP = Declined to Publish. (Source: vendors

From "Chart Watch: Embedded Processors," Microprocessor Report, August 25, 2003

CS 152 L04 Logic (23) Patterson Fall 2003 © UCB

### Die Yield: 1995 data

#### Raw Dice Per Wafer

| wafer diameter | d          | ie area ( | mm²) |     |     |     |

|----------------|------------|-----------|------|-----|-----|-----|

|                | <u>100</u> | 144       | 196  | 256 | 324 | 400 |

| 6"/15cm        | 139        | 90        | 62   | 44  | 32  | 23  |

| 8"/20cm        | 265        | 177       | 124  | 90  | 68  | 52  |

| 10"/25cm       | 431        | 290       | 206  | 153 | 116 | 90  |

| die yield      | 23%        | 19%       | 16%  | 12% | 11% | 10% |

typical CMOS process:  $\alpha$  =2, wafer yield=90%, defect density=2/cm2, 4 test sites/wafer

#### **Good Dice Per Wafer (Before Testing!)**

| 6"/15cm  | 31 | 16        | 9  | 5  | 3  | 2 |

|----------|----|-----------|----|----|----|---|

| 8"/20cm  | 59 | <b>32</b> | 19 | 11 | 7  | 5 |

| 10"/25cm | 96 | 53        | 32 | 20 | 13 | 9 |

typical cost of an 8", 4 metal layers, 0.5um CMOS wafer: ~\$2000

CS 152 L04 Logic (24) Patterson Fall 2003 © UCB

# Real World Examples: 1993

| Chip    | Metal<br>layers | Line<br>width | Wafer<br>cost | Defect<br>/cm² | Area<br>mm² | Dies/<br>wafer | Yield | Die Cost |

|---------|-----------------|---------------|---------------|----------------|-------------|----------------|-------|----------|

| 386DX   | 2               | 0.90          | \$900         | 1.0            | 43          | 360            | 71%   | \$4      |

| 486DX2  | 3               | 0.80          | \$1200        | 1.0            | 81          | 181            | 54%   | \$12     |

| PowerP( | C 601 4         | 0.80          | \$1700        | 1.3            | 121         | 115            | 28%   | \$53     |

| HP PA 7 | 100 3           | 0.80          | \$1300        | 1.0            | 196         | 66             | 27%   | \$73     |

| DEC Alp | ha 3            | 0.70          | \$1500        | 1.2            | 234         | 53             | 19%   | \$149    |

| SuperSF | PARC 3          | 0.70          | \$1700        | 1.6            | 256         | 48             | 13%   | \$272    |

| Pentium | 3               | 0.80          | \$1500        | 1.5            | 296         | 40             | 9%    | \$417    |

From "Estimating IC Manufacturing Costs," by Linley Gwennap, *Microprocessor Report*, August 2, 1993, p. 15

Patterson Fall 2003 © UCB

CS 152 L04 Logic (25)

### **Other Costs**

IC cost = Die cost + Testing cost + Packaging cost

Final test yield

Packaging Cost: depends on pins, heat dissipation

| Chip        | Die Package |      |      |             | Test &      | Total      |

|-------------|-------------|------|------|-------------|-------------|------------|

|             | cost        | pins | type | cost        | Assembly    |            |

| 386DX       | \$4         | 132  | QFP  | <b>\$1</b>  | \$4         | <b>\$9</b> |

| 486DX2      | <b>\$12</b> | 168  | PGA  | <b>\$11</b> | \$12        | \$35       |

| PowerPC 601 | <b>\$53</b> | 304  | QFP  | \$3         | <b>\$21</b> | \$77       |

| HP PA 7100  | <b>\$73</b> | 504  | PGA  | \$35        | \$16        | \$124      |

| DEC Alpha   | \$149       | 431  | PGA  | \$30        | <b>\$23</b> | \$202      |

| SuperSPARC  | \$272       | 293  | PGA  | <b>\$20</b> | \$34        | \$326      |

| Pentium     | \$417       | 273  | PGA  | <b>\$19</b> | \$37        | \$473      |

CS 152 L04 Logic (26) Patterson Fall 2003 © UCB

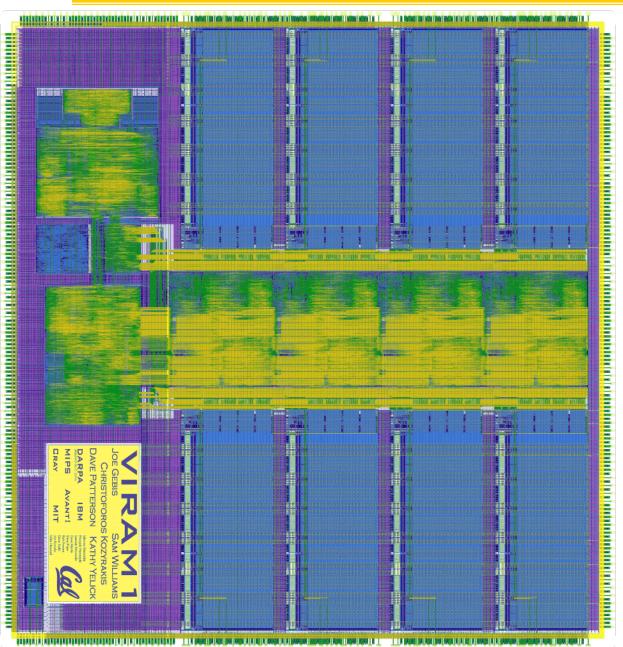

# **Berkeley Vector IRAM chip: 2003**

- MIPS CPU + multimedia coprocessor + 104 Mbits (13 Mbytes) of on-chip main memory

- °2 W, 200 MHz

- °Die size: 325 mm², in 0.18 micron, 125M transistors

- °App: future PDAs

### **Peer Instruction**

° Which of the following are <u>false</u>?

**1.**

$$(\overline{A} + \overline{B}) \cdot (\overline{C} + \overline{D}) = (\overline{A} \cdot \overline{B}) + (\overline{C} + \overline{D})$$

- 2. Clock skew can lead to setup time violations

- 3. Clock skew can lead to hold time violations

- 4. If the die size is doubled, the cost of the die is roughly quadrupled

152 L04 Logic (28) Patterson Fall 2003 © UCB

### In conclusion, Logic review ...

- ° Critical Path is longest among N parallel paths

- Setup Time and Hold Time determine how long Input must be stable before and after trigger clock edge

- Clock skew is difference between clock edge in different parts of hardware; it affects clock cycle time and can cause hold time, setup time violations

- \*FSM specify control symbolically

- Moore machine easiest to understand, debug

- "One shot" reduces decoding for faster FSM

- ° Die size affects both dies/wafer and yield

CS 152 L04 Logic (29) Patterson Fall 2003 © UCB