# CS152 – Computer Architecture and Engineering

Lecture 10 – Introduction to Pipelining 2003-09-24

Dave Patterson (www.cs.berkeley.edu/~patterson)

www-inst.eecs.berkeley.edu/~cs152/

Patterson Fall 2003 © I

# Review (1 of 4)

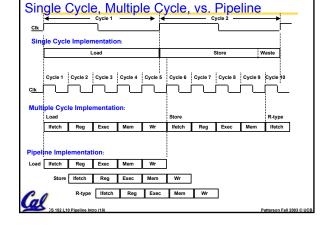

- · Disadvantages of the Single Cycle Processor

- Long cycle time

- Cycle time is too long for all instructions except the Load

- No reuse of hardware

- · Multiple Cycle Processor:

- Divide the instructions into smaller steps

- Execute each step (instead of the entire instruction) in one cycle

- Partition datapath into equal size chunks to minimize cycle time

- ~10 levels of logic between latches

- Follow same 5-step method for designing "real" processor

Patterson Fall 2003 © UCE

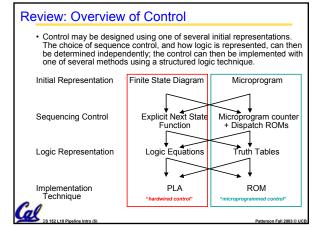

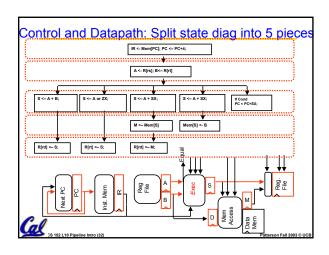

### Review (2 of 4)

- · Control is specified by finite state diagram

- Specialized state-diagrams easily captured by microsequencer

- simple increment & "branch" fields

- datapath control fields

- · Control is more complicated with:

- complex instruction sets

- restricted datapaths (see the book)

- · Control design can become Microprogramming

Patterson Fall 2003 © UC

# Summary (3 of 4)

- · Microprogramming is a fundamental concept

- implement an instruction set by building a very simple processor and interpreting the instructions

- essential for very complex instructions and when few register transfers are possible

- Control design reduces to Microprogramming

- Design of a Microprogramming language

- Start with list of control signals

- Group signals together that make sense (vs. random): called "fields"

- Place fields in some logical order (e.g., ALU operation & ALU operands first and microinstruction sequencing last)

- To minimize the width, encode operations that will never be used at the same time

- Create a symbolic legend for the microinstruction format, showing name of field values and how they set the control signals

CS 152 L10 Pipeline Intro (4)

Patterson Fall 2003 ©

#### Administrivia

- · Office hours in Lab

- Mon 4 5:30 Jack, Tue 3:30-5 Kurt,

Wed 3 4:30 John, Thu 3:30-5 Ben

- Dave's office hours Tue 3:30 5

- · Lab 3 demo Friday, due Monday

- · Reading Chapter 6, sections 6.1 to 6.4

- Midterm Wed Oct 8 5:30 8:30 in 1 LeConte

- Midterm review Sunday Oct 4, 5 PM in 306 Soda

- Bring 1 page, handwritten notes, both sides

- Meet at LaVal's Northside afterwards for Pizza

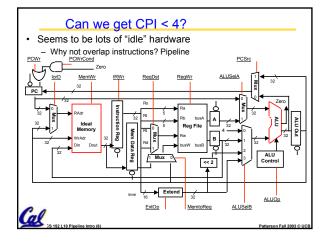

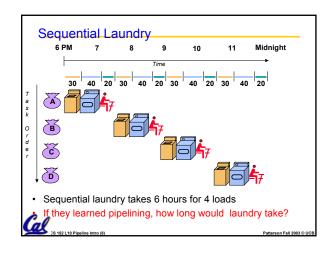

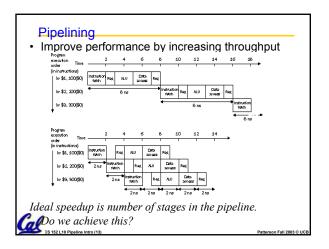

# Why Pipeline?

- Suppose we execute 100 instructions

- Single Cycle Machine

- $-4.5 \text{ ns/cycle } \times 1 \text{ CPI } \times 100 \text{ inst} = 450 \text{ ns}$

- · Multicycle Machine

- 1.0 ns/cycle x 4.1 CPI (due to inst mix) x 100 inst = 410 ns

- · Ideal pipelined machine

- 1.0 ns/cycle x (1 CPI x 100 inst + 4 cycle fill) = 104 ns

atterson Fall 2003 © I

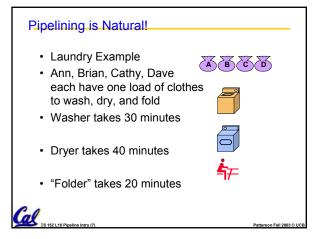

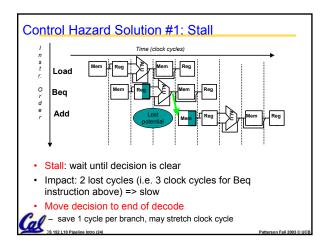

# Can pipelining get us into trouble?

- · Yes: Pipeline Hazards

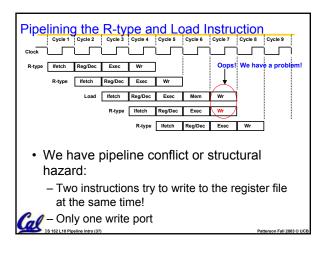

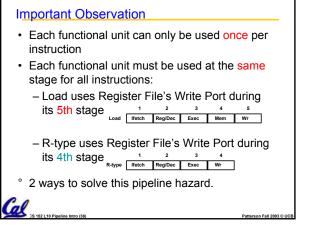

- structural hazards: attempt to use the same resource two different ways at the same time

- E.g., combined washer/dryer would be a structural hazard or folder busy watching TV

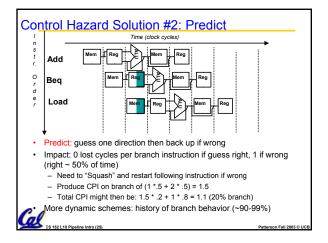

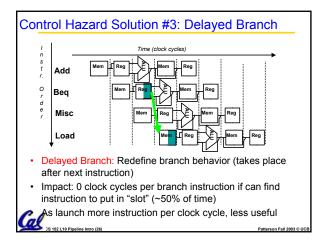

- control hazards: attempt to make a decision before condition is evaluated

- E.g., washing football uniforms and need to get proper detergent

- level; need to see after dryer before next load in

branch instructions

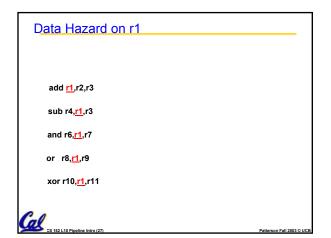

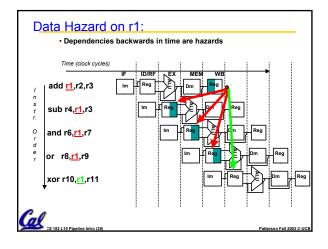

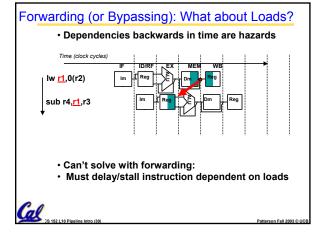

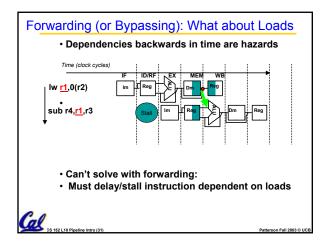

- data hazards: attempt to use item before it is ready

- E.g., one sock of pair in dryer and one in washer; can't fold until get sock from washer through dryer

- instruction depends on result of prior instruction still in the pipeline

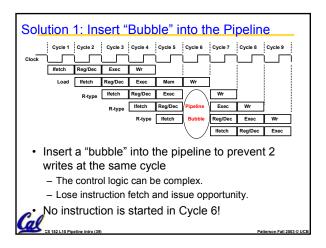

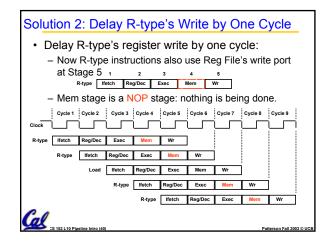

- Can always resolve hazards by waiting

- pipeline control must detect the hazard

- take action (or delay action) to resolve hazards

Patterson Fall 2003 © U

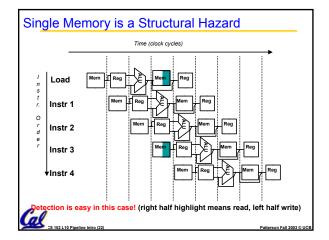

# Structural Hazards limit performance

- Example: if 1.3 memory accesses per instruction and only one memory access per cycle then

- average CPI ≥ 1.3

- otherwise resource is more than 100% utilized

- One Structural Hazard solution: more resources

- Instruction cache and Data cache

Patterson Fall 2003 © UCB

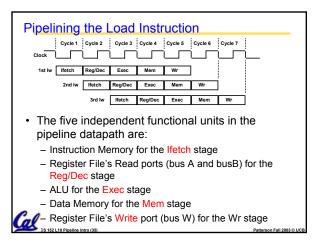

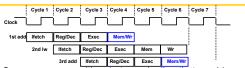

# Peer Instruction Cycle 1 Cycle 2 Cycle 3 Cycle 4 Cycle 5 Cycle 6 Cycle 7 Clock 1st lw Iffetch Reg/Dec Exec Mem1 Mem2 Wr 2nd lw Iffetch Reg/Dec Exec Mem1 Mem2 Wr 3rd lw Iffetch Reg/Dec Exec Mem1 Mem2 Wr

- Suppose a big (overlapping) data cache results in a data cache latency of 2 clock cycles and a 6-stage pipeline. What is the impact?

- 1. Instruction bandwidth is now 5/6-ths of the 5-stage pipeline

- 2. Instruction bandwidth is now 1/2 of the 5-stage pipeline

- 3. The branch delay slot is now 2 instructions

- 4. The load-use hazard can be with 2 instructions following load

- 5. Both 3 and 4: branch delay and load-use now 2 instructions

6. None of the above

S 152 I 10 Pineline Intro (43)

Patterson Fall 2003 © II

#

- Suppose a big (overlapping) I cache results in a licache latency of 2 clock cycles and a 6-stage pipeline. What is the impact?

- 1. Instruction bandwidth is now 5/6-ths of the 5-stage pipeline

- 2. Instruction bandwidth is now 1/2 of the 5-stage pipeline

- 3. The branch delay slot is now 2 instructions

- 4. The load-use hazard can be with 2 instructions following load

- 5. Both 3 and 4: branch delay and load-use now 2 instructions

- 6. None of the above

Patterson Fall 2003 © HC

#### Peer Instruction

- Suppose we use with a 4 stage pipeline that combines memory access and write back stages for all instructions but load, stalling when there are structural hazards. Impact?

- 1. The branch delay slot is now 0 instructions

- 2. Every load stalls since it has a structural hazard

- 3. Every store stalls since it has a structural hazard

- 4. Both 2 & 3: loads & stores stall due to structural hazards

- 5. Every load stalls, but there is no load-use hazard anymore

- 6. Both 2 & 3, but there is no load-use hazard anymore

- 7. None of the above

Patterson Fall 2

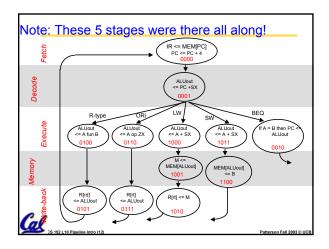

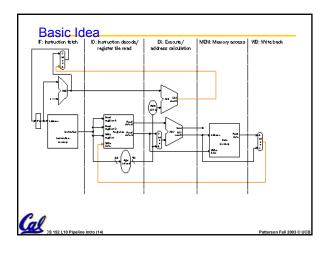

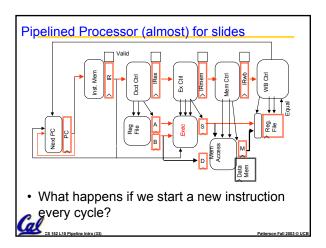

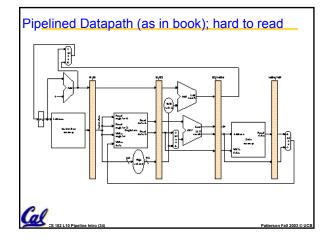

# Designing a Pipelined Processor

- Go back and examine your datapath and control diagram

- Associate resources with states

- Ensure that backwards flows do not conflict, or figure out how to resolve

- Assert control in appropriate stage

tterson Fall 2003 (

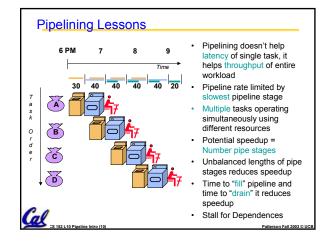

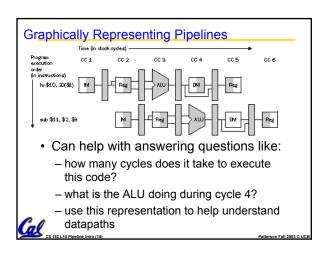

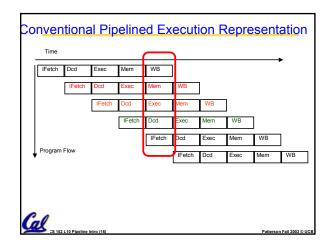

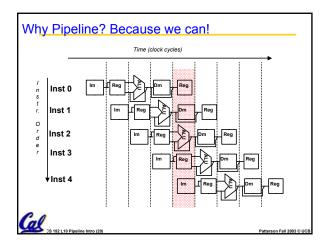

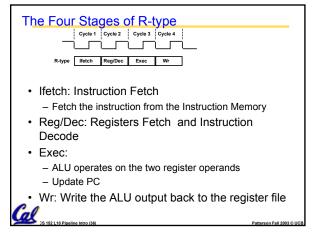

#### Summary: Pipelining

- · Reduce CPI by overlapping many instructions

- Average throughput of approximately 1 CPI with fast clock

- · Utilize capabilities of the Datapath

- start next instruction while working on the current one

- limited by length of longest stage (plus fill/flush)

- detect and resolve hazards

- · What makes it easy

- all instructions are the same length

- just a few instruction formats

- memory operands appear only in loads and stores

- What makes it hard?

- structural hazards: suppose we had only one memory

- control hazards: need to worry about branch instructions

- data hazards: an instruction depends on a previous instruction

Patterson Fall 2003 © UCE