# CS152 – Computer Architecture and Engineering

Lecture 12 - Control Wrap up: Microcode, Interrupts, RAW/WAR/WAW

2003-10-02

#### Dave Patterson

(www.cs.berkeley.edu/~patterson)

www-inst.eecs.berkeley.edu/~cs152/

\_ .. \_ .....

### **Pipelining Review**

- What makes it easy

- all instructions are the same length

- just a few instruction formats

- memory operands appear only in loads and stores

- · Hazards limit performance

- Structural: need more HW resources

- Data: need forwarding, compiler scheduling

- Control: early evaluation & PC, delayed branch, prediction

- · Data hazards must be handled carefully:

- RAW data hazards handled by forwarding

- WAW and WAR hazards don't exist in 5-stage pipeline

- MIPS I instruction set architecture made pipeline visible (delayed branch, delayed load)

- · More performance from deeper pipelines, parallelism

S 152 L12 Micrcode, Interrrupts (2)

Patterson Fall 2003 © U

#### Outline

- RAW, WAR, WAW: 2nd Try

- · Interrupts and Exceptions in MIPS

- How to handle them in multicycle control?

- What about pipelining and interrupts?

- · Microcode: do it yourself microprogramming

atterson Fall 2003 © UC

## 3 Generic Data Hazards: RAW, WAR, WAW

Read After Write (RAW)

Instr<sub>J</sub> tries to read operand before Instr<sub>I</sub> writes it

```

I: add r1,r2,r3

J: sub r4,r1,r3

```

- Caused by a "Dependence" (in compiler nomenclature). This hazard results from an actual need for communication.

- Forwarding handles many, but not all, RAW dependencies in 5 stage MIPS pipeline

SS 152 L12 Micrcode, Interrrupts (4)

Patterson Fall 2003 ©

## 3 Generic Data Hazards: RAW, WAR, WAW

Write After Read (WAR)

Instr. writes operand *before* Instr. reads it

I: sub r4,r1,r3 J: add r1,r2,r3 K: mul r6,r1,r7

- Called an "anti-dependence" by compiler writers. This results from "reuse" of the name "r1".

- · Can't happen in MIPS 5 stage pipeline because:

- All instructions take 5 stages, and

- Reads are always in stage 2, and

- Writes are always in stage 5

al

Patterson Fall 2003 © UCE

## 3 Generic Data Hazards: RAW, WAR, WAW

Write After Write (WAW)

Instr. writes operand before Instr. writes it.

```

I: sub r1,r4,r3

J: add r1,r2,r3

K: mul r6,r1,r7

```

- Called an "output dependence" by compiler writers

This also results from the "reuse" of name "r1".

- Can't happen in MIPS 5 stage pipeline because:

- All instructions take 5 stages, and

- Writes are always in stage 5

- · Can see WAR and WAW in more complicated pipes

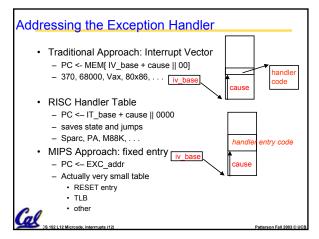

#### Two Types of Exceptions: Interrupts and Traps Interrupts caused by external events: Network, Keyboard, Disk I/O, Timer asynchronous to program execution Most interrupts can be disabled for brief periods of time · Some (like "Power Failing") are non-maskable (NMI) - may be handled between instructions - simply suspend and resume user program Traps caused by internal events · exceptional conditions (overflow) · errors (parity) · faults (non-resident page) synchronous to program execution - condition must be remedied by the handler instruction may be retried or simulated and program continued or program may be aborted

## Saving State

- · Push it onto the stack

- Vax. 68k. 80x86

- · Shadow Registers

- M88k

- Save state in a shadow of the internal pipeline registers

- Save it in special registers

- MIPS EPC, BadVaddr, Status, Cause

## Additions to MIPS ISA to support Exceptions?

- · Exception state is kept in "coprocessor 0".

- Use mfc0 read contents of these registers

- Every register is 32 bits, but may be only partially defined BadVAddr (register 8)

- register contained memory address at which memory reference occurred

Status (register 12)

- interrupt mask and enable bits

Cause (register 13)

- the cause of the exception

- Bits 6 to 2 of this register encodes the exception type (e.g. undefined instruction=10 and arithmetic overflow=12)

EPC (register 14)

- address of the affected instruction (register 14 of coprocessor 0).

- · Control signals to write BadVAddr, Status, Cause, and EPC

- Be able to write exception address into PC (8000 0180<sub>hex</sub>)

- May have to undo PC = PC + 4, since want EPC to point to offending

- instruction (not its successor): PC = PC 4

## Details of Status register: MIPS I

5 4 3 2 1 0 k e k e k e Status Mask old prev

- Mask = 1 bit for each of 5 hardware and 3 software interrupt levels

- 1 => enables interrupts

- 0 => disables interrupts

- k = kernel/user

- 0 => was in the kernel when interrupt occurred

- 1 => was running user mode

- e = interrupt enable

- 0 => interrupts were disabled 1 => interrupts were enabled

- When interrupt occurs, 6 LSB shifted left 2 bits, setting 2 LSB to 0

- run in kernel mode with interrupts disabled

## Details of Status register: MIPS 32

3 2 1 0 Status Mask mode e

- Mask = 1 bit for each of 5 hardware and 3 software interrupt levels

- 1 => enables interrupts

- 0 => disables interrupts

- mode = kernel/user

- 0 => was in the kernel when interrupt occurred

- 2 => was running user mode

- (added 1 for "supervisor" state)

- e = interrupt enable

- 0 => interrupts were disabled

- 1 => interrupts were enabled

#### Details of Cause register

10 6 Status Pending Code

- Pending interrupt 5 hardware levels: bit set if interrupt occurs but not yet serviced

- handles cases when more than one interrupt occurs at same time, or while records interrupt requests when interrupts disabled

- Exception Code encodes reasons for interrupt

- 0 (INT) => external interrupt

- 4 (ADDRL) => address error exception (load or instr fetch)

- 5 (ADDRS) => address error exception (store)

- 6 (IBUS) => bus error on instruction fetch

- 7 (DBUS) => bus error on data fetch

- 8 (Syscall) => Syscall exception

- 9 (BKPT) => Breakpoint exception

- 10 (RI) => Reserved Instruction exception

- 12 (OVF) => Arithmetic overflow exception

#### Part of the handler in trap handler.s .ktext 0x80000080 entry: .set noat move \$k1 \$at .set at sw \$v0 s1 sw \$a0 s2 mfc0 \$k0 \$13 # Not re-entrent and we can't trust \$sp # Cause # syscall 4 (print\_str) li \$v0 4 la \$a0 \_\_m1\_ li \$v0 1 # syscall 1 (print\_int) \$a0 \$k0 2 # shift Cause reg srl svscall ret: lw \$v0 s1 mfc0 \$k0 \$14 set noat move \$at \$k1 # Restore \$at Return from exception handler c0 \$k0 4 # Return to next instruction

#### Administrivia

- Lab 4 demo Mon 10/13, write up Tue 10/14

- Reading Ch 5: 5.1 to 5.8, Ch 6: 6.1 to 6.7

- Midterm Wed Oct 8 5:30 8:30 in 1 LeConte

- Midterm review Sunday Oct 4, 5 PM in 306 Soda

- Bring 1 page, handwritten notes, both sides

- Meet at LaVal's Northside afterwards for Pizza

- No lecture Thursday Oct 9

- Office hours

- Mon 4 5:30 Jack, Tue 3:30-5 Kurt, Wed 3 - 4:30 John, Thu 3:30-5 Ben

Dave's office hours Tue 3:30 – 5

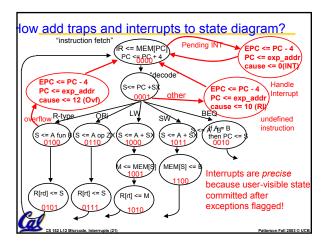

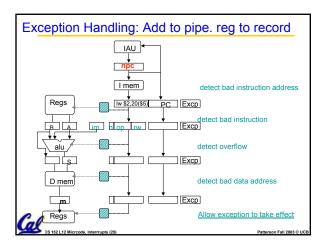

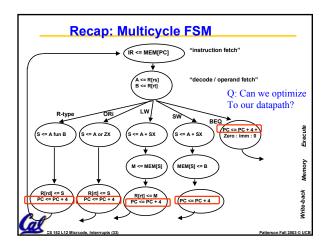

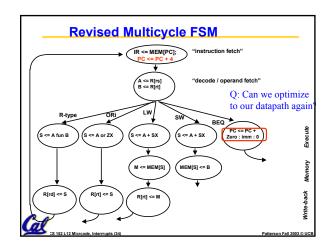

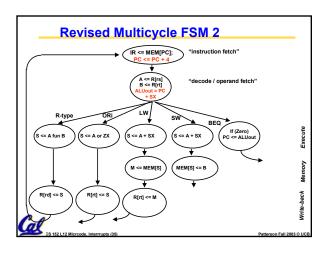

## Example: How Control Handles Traps in our FSD

- Undefined Instruction-detected when no next state is defined from state 1 for the op value.

- We handle this exception by defining the next state value for all op values other than lw, sw, 0 (R-type), jmp, beq, and ori as new state 12.

- Shown symbolically using "other" to indicate that the op field does not match any of the opcodes that label arcs out of state 1.

- Arithmetic overflow-detected on ALU ops such as signed add

- Used to save PC and enter exception handler

- External Interrupt flagged by asserted interrupt line

- Again, must save PC and enter exception handler

- Note: Challenge in designing control of a real machine is to handle different interactions between instructions and other exception-causing events such that control logic remains small and fast.

- Complex interactions makes the control unit the most challenging aspect of hardware design

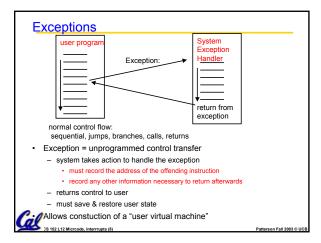

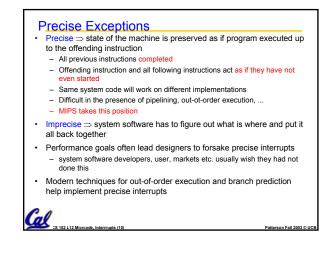

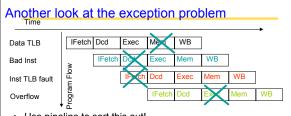

### Exception/Interrupts and Pipelining

5 instructions, executing in 5 different pipeline stages!

· Who caused the interrupt?

Stage Problem interrupts/Exceptions occurring

- Page fault on instruction fetch; misaligned memory access; memory-protection violation

- Undefined (or illegal) opcode ID

- EX Arithmetic exception

MEM Page fault on data fetch; misaligned memory access; memory-protection violation; memory error

- · How do we stop the pipeline? How do we restart it?

- · Do we interrupt immediately or wait?

- · How do we sort all of this out to maintain preciseness?

- · Use pipeline to sort this out!

- Pass exception status along with instruction.

- Keep track of PCs for every instruction in pipeline.

- Don't act on exception until it reache WB stage

- · Handle interrupts through "faulting noop" in IF stage

- When instruction reaches end of MEM stage:

- Save PC  $\Rightarrow$  EPC, Interrupt vector addr  $\Rightarrow$  PC

- Turn all (partially-executed) succeeding instructions into noops!

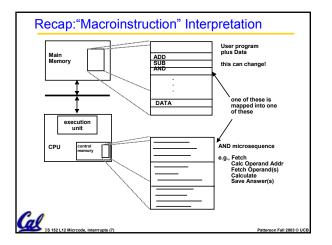

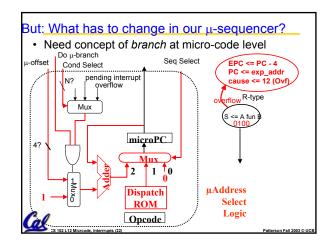

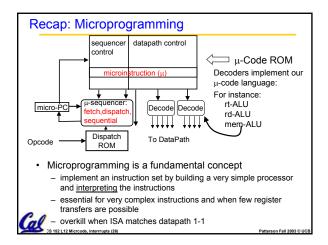

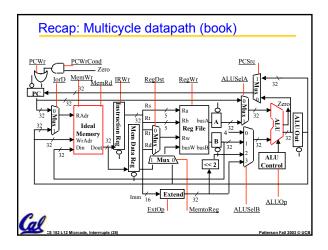

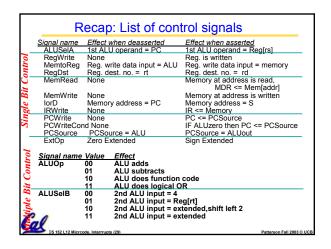

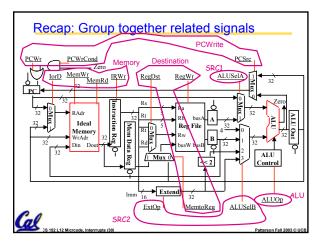

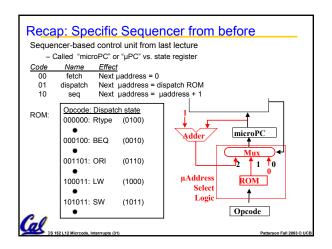

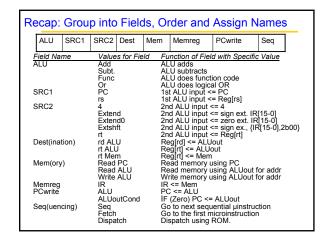

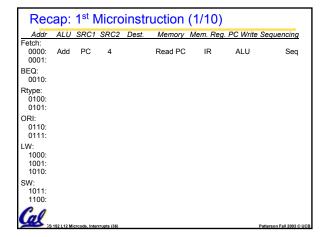

## Recap: Microprogramming

- Microprogramming is a convenient method for implementing structured control state diagrams:

- Random logic replaced by microPC sequencer and ROM

- Each line of ROM called a μinstruction: contains sequencer control + values for control points

- limited state transitions: branch to zero, next sequential, branch to μinstruction address from displatch ROM

- Design of a Microprogramming language

- Start with list of control signals

- 2. Group signals together that make sense (vs. random): called "fields"

- 3. Place fields in some logical order (e.g., ALU operation & ALU operands first and microinstruction sequencing last)

- To minimize the width, encode operations that will never be used at the same time.

- Create a symbolic legend for the microinstruction format, showing name of field values and how they set the control signals

#### Legacy Software and Microprogramming

- IBM bet company on 360 Instruction Set Architecture (ISA): single instruction set for many classes of machines

- (8-bit to 64-bit)

- Stewart Tucker stuck with job of what to do about software compatibility

- If microprogramming could easily do same instruction set on many different microarchitectures, then why couldn't multiple microprograms do multiple instruction sets on the same microarchitecture?

- Coined term "emulation": instruction set interpreter in microcode for non-native instruction set

- Very successful: in early years of IBM 360 it was hard to know whether old instruction set or new instruction set

was more frequently used

Patterson Fall 2003 © UC

## Microprogramming Pros and Cons

- · Ease of design

- Flexibility

- Easy to adapt to changes in organization, timing, technology

- Can make changes late in design cycle, or even in the field

- Can implement very powerful instruction sets (just more control memory)

- Generality

- Can implement multiple instruction sets on same machine.

- Can tailor instruction set to application

- Compatibility

- Many organizations, same instruction set

- · Costly to implement

- Slow

#### Thought: Microprogramming one inspiration for RISC

- If simple instruction could execute at very high clock rate...

- If you could even write compilers to produce microinstructions...

- If most programs use simple instructions and addressing modes...

- If microcode is kept in RAM instead of ROM so as to fix bugs ...

- If same memory used for control memory could be used instead as cache for "macroinstructions"...

- Then why not skip instruction interpretation by a microprogram and simply compile directly into lowest language of machine? (microprogramming is overkill when ISA matches datapath 1-1)

CS 152 L12 Micrcode, Interrrupts (5

Patterson Fall 2003 ©

#### Summary

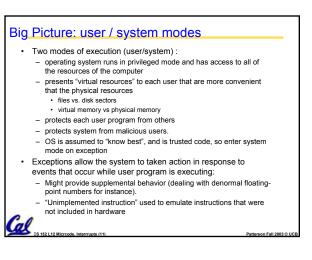

- Exceptions, Interrupts handled as unplanned procedure calls

- Control adds arcs to check for exceptions, new states to adjust PC, set CPU status

- OS implements interrupt/exception policy (priority levels) using Interrupt Mask

- For pipelining, interrupts need to be precise (like multicycle)

- · Control design can reduces to Microprogramming

- · Control is more complicated with:

- complex instruction sets

- restricted datapaths (see the book)

Patterson Fall 2003 © UCE